22.02.2013

# **Revision Record**

| DATE       | VER. | DESRIPTION                     | NOTE |

|------------|------|--------------------------------|------|

| 07.02.2013 | 0    | Specification released         | -    |

| 22.02.2013 | 1    | Revise Optical Characteristics | -    |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

|            |      |                                |      |

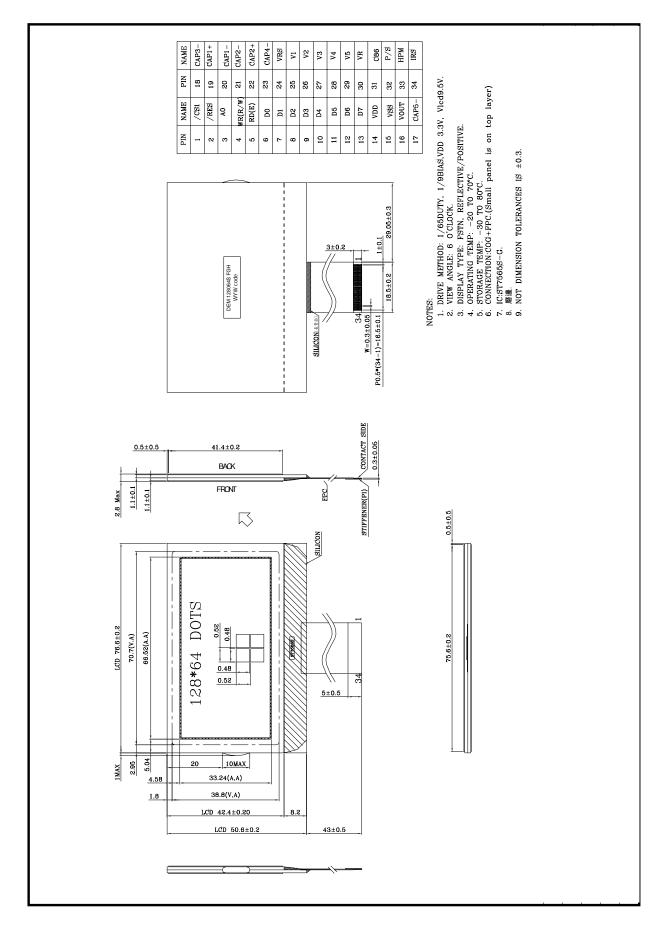

# **LCM Dimension**

#### CONTENTS

| 1. | PRC | DUCT SPECIFICATIONS                              | 5  |

|----|-----|--------------------------------------------------|----|

|    | 1.1 | General                                          | 5  |

|    | 1.2 | Mechanical Characteristics                       | 5  |

|    | 1.3 | Absolute Maximum Ratings                         | 6  |

|    | 1.4 | Electrical Characteristics                       | 6  |

|    | 1.5 | Optical Characteristics Absolute maximum ratings | 6  |

|    | 1.6 | Optical Characteristics                          | 7  |

|    | 1.7 | LED Back-light Characteristics                   | 8  |

| 2. | REL | JABILITY                                         | 9  |

| 3. | OPE | ERATING INSTRUCTIONS                             | 10 |

|    | 3.1 | Input signal Function                            | 10 |

|    | 3.2 | Voltage Generator Circuit                        | 12 |

|    | 3.3 | Timing Diagram                                   | 14 |

| 4. | NO  | ΓES                                              | 17 |

# **1. PRODUCT SPECIFICATIONS**

#### 1.1 General

- 128 x 64 dot matrix LCD

- FSTN, Positive Mode

- Reflective, Wide Temperature Range

- 6 o'clock

- Backlight: No Backlight

- Multiplexing Driving : 1/65duty, 1/9bias

- Controller IC: ST7565S-G (Sitronix)

## 1.2 Mechanical Characteristics

| Item                                                         | Characteristic            |

|--------------------------------------------------------------|---------------------------|

| Dot configuration                                            | 128 x 64                  |

| Dot dimensions(mm)                                           | 0.48 x 0.48               |

| Dot spacing (mm)                                             | 0.52 x 0.52               |

| Module dimensions (Horizontal ×<br>Vertical × Thickness, mm) | 76.60 x 50.60 x 2.80 max. |

| Viewing area (Horizontal ×<br>Vertical, mm)                  | 70.70 x 38.80             |

| Active area (Horizontal × Vertical, mm)                      | 66.52 x 33.24             |

1.3 Absolute Maximum Ratings

| Characteristic            | Symbol          | Unit | Value                        |

|---------------------------|-----------------|------|------------------------------|

| Operating Voltage (logic) | V <sub>DD</sub> | V    | -0.3 to +5.0                 |

| Input Voltage             | V <sub>IN</sub> | V    | -0.3 to V <sub>DD</sub> +0.3 |

Note 1: Referenced to  $V_{SS}=0V$

#### 1.4 Electrical Characteristics

| Characteristic              | Symbol                           | Condition                        | Min.               | Тур. | Max.               | Unit         |

|-----------------------------|----------------------------------|----------------------------------|--------------------|------|--------------------|--------------|

| Operating<br>Voltage(logic) | V <sub>DD</sub> -V <sub>SS</sub> |                                  | 3.0                | 3.3  | 3.6                | V            |

| Innut Voltago               | V <sub>IH</sub>                  |                                  | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | $\mathbf{V}$ |

| Input Voltage               | V <sub>IL</sub>                  |                                  | V <sub>SS</sub>    |      | 0.2V <sub>DD</sub> | v            |

| Output Voltogo              | V <sub>OH</sub>                  | I <sub>OH</sub> =-0.1mA          | 0.8V <sub>DD</sub> |      | V <sub>DD</sub>    | v            |

| Output Voltage              | V <sub>HL</sub>                  | I <sub>OL</sub> =0.1mA           | V <sub>SS</sub>    |      | 0.2V <sub>DD</sub> | v            |

| Current<br>Consumption      | I <sub>DD</sub>                  | V <sub>IN</sub> =V <sub>DD</sub> |                    | 0.05 | 1                  | mA           |

1.5 Optical Characteristics Absolute Maximum Ratings

| Item                        | Symbol | Rating | Unit |

|-----------------------------|--------|--------|------|

| Operating temperature range | Тор    | -20~70 | °C   |

| Storage temperature range   | Tst    | -30~80 | °C   |

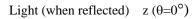

$\theta 2$

#### **1.6 Optical Characteristics**

|                                                                                                                         |             |                                         | 1/00 44    | <i>cj</i> , <i>i//oiu</i> . | , , , , , , , , , , , , , , , , , , , , | 5 <b>(</b> , 1 <b>u</b> -25 |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|------------|-----------------------------|-----------------------------------------|-----------------------------|--|

| Item                                                                                                                    | Symbol      | Conditions                              | Min.       | Тур.                        | Max                                     | Reference                   |  |

|                                                                                                                         | Vlcd=VDD-VO |                                         | 9.2        | 9.5                         | 9.8                                     | V                           |  |

| Driving voltage                                                                                                         |             | -20°C                                   | 9.5        | 9.8                         | 10.1                                    | V                           |  |

| Driving voltage                                                                                                         | Vlcd        | +25°C                                   | °C 9.2 9.5 |                             | 9.8                                     | V                           |  |

|                                                                                                                         |             | +70°C                                   | 8.9        | 9.2                         | 9.5                                     | V                           |  |

| Viewing angle                                                                                                           | θ           | C≥2.0,∅=0°C                             | 30°        | -                           |                                         | Notes 1 & 2                 |  |

| Contrast                                                                                                                | С           | θ=5°, Ø=0°                              | 3.0        |                             | -                                       | Note 3                      |  |

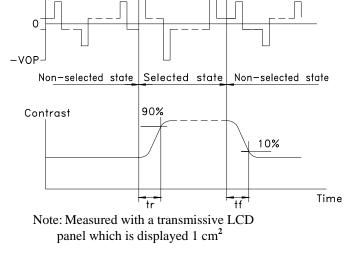

| Response time(rise)                                                                                                     | ton         | $\theta=5^{\circ}, \emptyset=0^{\circ}$ | -          |                             | 198ms                                   | Note 4                      |  |

| Response time(fall)                                                                                                     | toff        | $\theta=5^{\circ}, \emptyset=0^{\circ}$ | -          | -                           | 176ms                                   | Note 4                      |  |

| Note 1: Definition of angles $\theta$ and $\emptyset$ Note 2: Definition of viewing angles $\theta$ 1 and $\emptyset$ 2 |             |                                         |            |                             |                                         |                             |  |

Cmax.

2.0

θ1

Contrast

С

1/65 duty, 1/9bias, Vlcd=9.5V, Ta=25

$Y(\emptyset=0\circ)$ Light (when transmitted ) (θ=90°)

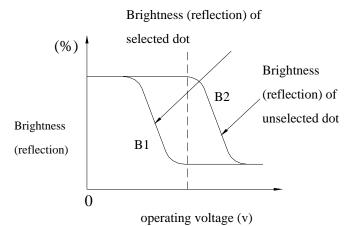

#### Note 3: Definition of contrast C

$$C = \frac{Brightness (reflection) of unselected dot (B2)}{Brightness (reflection) of selected dot (B1)}$$

viewing angle  $\theta$  ( $\Phi$ fixed)

Optimum viewing angle with the

naked eye and viewing angle  $\theta$  at

V OPR : Operating voltage f <sub>FRM</sub> : Frame frequency t <sub>ON</sub> : Response time (rise) t <sub>OFF</sub> : Response time (fall)

Cmax. Above are not always the same Note 4: Definition of response time

VOP

Note :

Version: 1

# 2. RELIABILITY

## 2.1 Reliability

| Test item                                        | Test condition                                                                                        | Evaluation and assessment                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Operation at high<br>temperature and<br>humidity | 40 °C±2 °C<br>90%RH for 500hours                                                                      | No abnormalities in<br>functions* and<br>appearance** |

| Operation at high temperature                    | 60 °C±2 °C for 500 hours                                                                              | No abnormalities in<br>functions* and<br>appearance** |

| Heat shock                                       | -20± ~ +60 °C Left for 1<br>hour at each temperature,<br>transition time 5 min,<br>repeated 10times   | No abnormalities in<br>functions* and<br>appearance** |

| Low temperature                                  | -20±2 °C for 500 hours                                                                                | No abnormalities in<br>functions* and<br>appearance** |

| Vibration                                        | Sweep for 1 min at 10 Hz,<br>55Hz, 10Hz, amplitude<br>1.5mm 2 hrs each in the<br>X,Y and Z directions | No abnormalities in<br>functions* and<br>appearance** |

| Drop shock                                       | Dropped onto a board from<br>a height of 10cm                                                         | No abnormalities in<br>functions* and<br>appearance** |

\* Dissipation current, contrast and display functions

\*\* Polarizing filter deterioration, other appearance defects

- 2.2 Liquid crystal panel service life 100,000 hours minimum at 25 °C±10 °C

- 2.3 definition of panel service life

- Contrast becomes 30% of initial value

- Current consumption becomes three times higher than initial value

- Remarkable alignment deterioration occurs in LCD cell layer

- Unusual operation occurs in display functions

# **3. OPERATING INSTRUCTIONS**

| 3.1 | Input Signal Function |

|-----|-----------------------|

|-----|-----------------------|

| Pin No | Symbol   | I/O      | Function                                                                     |  |  |  |  |  |

|--------|----------|----------|------------------------------------------------------------------------------|--|--|--|--|--|

|        | Cynibol  |          | This is the chip select signal. When $CS1 = "L"$ and $CS2 = "H,"$ then the   |  |  |  |  |  |

| 1      | /CS1     | I        | chip select becomes active, and data/command I/O is enabled.                 |  |  |  |  |  |

|        |          |          | When RES is set to "L," the settings are initialized. The reset operation    |  |  |  |  |  |

| 2      | /RES     | I        |                                                                              |  |  |  |  |  |

|        |          |          | is performed by the RES signal level.                                        |  |  |  |  |  |

|        |          |          | This is connect to the least significant bit of the normal MPU address       |  |  |  |  |  |

| 3      | A0       | I        | bus, and it determines whether the data bits are data or a command.          |  |  |  |  |  |

|        |          |          | A0 = "H": Indicates that D0 to D7 are display data.                          |  |  |  |  |  |

|        |          |          | A0 = "L": Indicates that D0 to D7 are control data.                          |  |  |  |  |  |

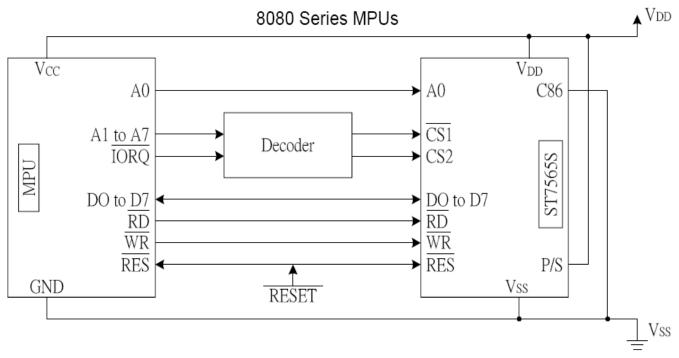

|        |          |          | <ul> <li>When connected to an 8080 MPU, this is active LOW.</li> </ul>       |  |  |  |  |  |

|        |          |          | (R/W) This terminal connects to the 8080 MPU WR signal. The signals          |  |  |  |  |  |

| 4      | WR(R/W)  |          | on the data bus are latched at the rising edge of the WR signal.             |  |  |  |  |  |

| 4      | ••••     | •        | <ul> <li>When connected to a 6800 Series MPU:</li> </ul>                     |  |  |  |  |  |

|        |          |          | This is the read/write control signal input terminal.                        |  |  |  |  |  |

|        |          |          | When R/W = "H": Read. When R/W = "L": Write.                                 |  |  |  |  |  |

|        |          |          | • When connected to an 8080 MPU, this is active LOW.                         |  |  |  |  |  |

|        |          |          | (E) This pin is connected to the RD signal of the 8080 MPU, and the          |  |  |  |  |  |

| 5      | RD(E)    |          | ST7565S series data bus is in an output status when this signal is "L".      |  |  |  |  |  |

|        |          |          | • When connected to a 6800 Series MPU, this is active HIGH.                  |  |  |  |  |  |

|        |          |          | This is the 6800 Series MPU enable clock input terminal.                     |  |  |  |  |  |

|        |          |          | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit |  |  |  |  |  |

|        |          |          | standard MPU data bus. When the serial interface is selected (P/S =          |  |  |  |  |  |

|        | D0 to D5 |          | "L"):                                                                        |  |  |  |  |  |

| 6~13   | D6 (SCL) | I/O      | D0 to D5 are set to high impedance.                                          |  |  |  |  |  |

|        | D7 (SI)  |          | D6 : the serial clock input (SCL) ; D7 : serial data input (SI) .            |  |  |  |  |  |

|        |          |          | When the chip select is not active, D0 to D7 are set to high impedance.      |  |  |  |  |  |

| 14     | VDD      | PS       | Shared with the MPU power supply terminal Vcc.                               |  |  |  |  |  |

| 15     | VSS      | PS       | This is a 0V terminal connected to the system GND.                           |  |  |  |  |  |

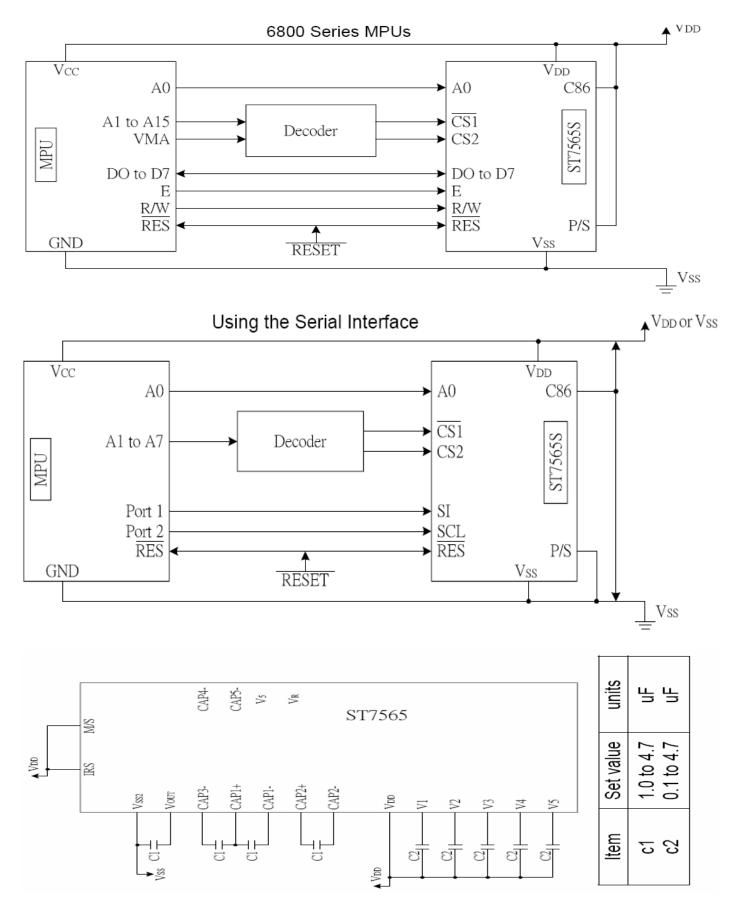

| 40     |          | 0        | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 16     | VOUT     | 0        | and VSS.                                                                     |  |  |  |  |  |

|        | a:==     | _        | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 17     | CAP5-    | 0        | and the CAP1+ terminal.                                                      |  |  |  |  |  |

|        |          |          | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 18     | CAP3-    | 0        | and the CAP1+ terminal.                                                      |  |  |  |  |  |

|        |          | <u> </u> | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 19     | CAP1+    | 0        | and the CAP1- terminal.                                                      |  |  |  |  |  |

|        |          | 1        | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 20     | CAP1-    | 0        | and the CAP1+ terminal.                                                      |  |  |  |  |  |

| 21     | CAP2-    | 0        | DC/DC voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

| 21     |          |          | Dorbo voltage converter. Connect a capacitor between this terminal           |  |  |  |  |  |

|       |                        |    | and th                                                              | ne CAP2+ termina                                                                             | al.           |                   |                   |            |  |  |  |

|-------|------------------------|----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|-------------------|-------------------|------------|--|--|--|

|       |                        |    |                                                                     | C voltage conver                                                                             | -             | ct a canacito     | r between this    | terminal   |  |  |  |

| 22    | CAP2+                  | 0  |                                                                     | e CAP2- termina                                                                              |               |                   |                   | torrinia   |  |  |  |

|       |                        |    |                                                                     |                                                                                              |               | ect a capacito    | r between this    | terminal   |  |  |  |

| 23    | CAP4-                  | 0  |                                                                     | DC/DC voltage converter. Connect a capacitor between this termina<br>and the CAP2+ terminal. |               |                   |                   |            |  |  |  |

|       |                        |    |                                                                     | is the internal-ou                                                                           |               |                   | oly for the ICI   |            |  |  |  |

| 24    | VRS                    | PS | suppl                                                               |                                                                                              |               |                   |                   | power      |  |  |  |

| 27    | VIXO                   | 10 |                                                                     | ,<br>je regulator.                                                                           |               |                   |                   |            |  |  |  |

|       |                        |    | -                                                                   | s a multi-level pov                                                                          |               | for the liquid e  | rvetal drivo. The | voltago    |  |  |  |

|       |                        |    |                                                                     | y applied is deter                                                                           |               |                   | •                 | -          |  |  |  |

|       |                        |    |                                                                     | gh the use of a re                                                                           |               |                   |                   |            |  |  |  |

|       | \/1\/2                 |    |                                                                     | lance using an o                                                                             |               | -                 | -                 |            |  |  |  |

| 25~29 | V1,V2,<br>V3,V4, V5    | PS |                                                                     | and must maintai                                                                             | •             | lage levels al    | e determined b    |            |  |  |  |

|       | v3,v <del>4</del> , v3 |    |                                                                     | ve magnitudes sho                                                                            |               |                   |                   |            |  |  |  |

|       |                        |    | rciativ                                                             |                                                                                              | Switt Delew.  |                   |                   |            |  |  |  |

|       |                        |    | VDD (= V0) ≧V1 ≧V2 ≧V3 ≧V4 ≧V5                                      |                                                                                              |               |                   |                   |            |  |  |  |

|       |                        |    | Output voltage regulator terminal. Provides the voltage between VDD |                                                                                              |               |                   |                   |            |  |  |  |

|       |                        |    | and                                                                 |                                                                                              |               |                   |                   |            |  |  |  |

| 30    | VR                     | Ι  | V5 th                                                               | V5 through a resistive voltage divider.                                                      |               |                   |                   |            |  |  |  |

|       |                        |    | IRS =                                                               | "L" : the V5 volta                                                                           | ge regulato   | or internal resis | stors are not us  | ed .       |  |  |  |

|       |                        |    | IRS =                                                               | "H" : the V5 volta                                                                           | ge regulato   | or internal resi  | stors are used .  |            |  |  |  |

|       |                        |    | This i                                                              | s the MPU interfa                                                                            | ce switch te  | erminal.          |                   |            |  |  |  |

| 31    | C86                    | Ι  | C86                                                                 | = "H": 6800 Ser                                                                              | ies MPU       | interface. (      | C86 = "L": 808    | 30 MPU     |  |  |  |

|       |                        |    | interfa                                                             | ace.                                                                                         |               |                   |                   |            |  |  |  |

|       |                        |    | This i                                                              | s the parallel data                                                                          | input/seria   | l data input sv   | witch terminal.   |            |  |  |  |

|       |                        |    | P/S =                                                               | "H": Parallel data                                                                           | input.        | P/S = "L": Ser    | ial data input.   |            |  |  |  |

|       |                        |    | The fo                                                              | ollowing applies d                                                                           | epending o    | n the P/S stat    | us:               |            |  |  |  |

|       |                        |    | P/S                                                                 | Data/Comman                                                                                  | Data          | Read/Write        | Serial Clock      |            |  |  |  |

| 32    | P/S                    | Ι  | "H"                                                                 | A0                                                                                           | D0 to D7      | RD, WR            | Х                 |            |  |  |  |

|       |                        |    | "L"                                                                 | A0                                                                                           | SI (D7)       | Write only        | SCL (D6)          |            |  |  |  |

|       |                        |    | Wher                                                                | P/S = "L", D0 to                                                                             | D5 may be     | "H", "L" or Op    | en.               |            |  |  |  |

|       |                        |    | RD (E                                                               | ) and WR (R/W)                                                                               | are fixed to  | either "H" or '   | 'L".              |            |  |  |  |

|       |                        |    | With s                                                              | serial data input, I                                                                         | t is impossi  | ible read data    | from RAM .        |            |  |  |  |

|       |                        |    | This i                                                              | s the power conti                                                                            | ol terminal   | for the power     | r supply circuit  | for liquid |  |  |  |

| 33    | /HPM                   | Ι  | crysta                                                              | l drive. /HPM =                                                                              | "H": Norma    | al mode /H        | HPM = "L": Hig    | h power    |  |  |  |

|       |                        |    | mode                                                                |                                                                                              |               |                   |                   |            |  |  |  |

|       |                        |    | This t                                                              | erminal selects th                                                                           | e resistors   | for the V5 vol    | tage level adjus  | tment.     |  |  |  |

|       |                        |    | IRS =                                                               | "H": Use the inte                                                                            | rnal resisto  | rs                |                   |            |  |  |  |

| 34    | IRS                    | Ι  | IRS =                                                               | "L": Do not use th                                                                           | ne internal   | resistors. The    | V5 voltage leve   | el is      |  |  |  |

|       |                        |    |                                                                     | ated by an exterr                                                                            | nal resistive | e voltage divi    | der attached to   | the VR     |  |  |  |

|       |                        |    | termir                                                              | nal                                                                                          |               |                   |                   |            |  |  |  |

# DEM 128064S FGH

# **Product Specification**

|                                            |      |     |    | Table ' | 1   |     |    |     |       |

|--------------------------------------------|------|-----|----|---------|-----|-----|----|-----|-------|

| P/S                                        | /CS1 | CS2 | A0 | /RD     | /WR | C86 | D7 | D6  | D5~D0 |

| H: Parallel Input                          | /CS1 | CS2 | A0 | /RD     | /WR | C86 | D7 | D6  | D5~D0 |

| L: Serial Input                            | /CS1 | CS2 | A0 | -       | —   | —   | SI | SCL | (HZ)  |

| "" indicates fixed to either "H" or to "L" |      |     |    |         |     |     |    |     |       |

to eitner H

| Table 2        |      |     |            |        |          |       |  |  |

|----------------|------|-----|------------|--------|----------|-------|--|--|

| C86 (P/S=H)    | /CS1 | CS2 | <b>A</b> 0 | E(/RD) | R/W(/WR) | D7~D0 |  |  |

| H: 6800 Series | /CS1 | CS2 | A0         | Е      | R/W      | D7~D0 |  |  |

| L: 8080 Series | /CS1 | CS2 | A0         | /RD    | /WR      | D7~D0 |  |  |

|        | Table 3     |             |     |                              |  |  |  |  |

|--------|-------------|-------------|-----|------------------------------|--|--|--|--|

| Shared | 6800 Series | 8080 Series |     | Eurotion                     |  |  |  |  |

| A0     | R/W         | /RD         | /WR | - Function                   |  |  |  |  |

| 1      | 1           | 0           | 1   | Reads the display data       |  |  |  |  |

| 1      | 0           | 1           | 0   | Writes the display data      |  |  |  |  |

| 0      | 1           | 0           | 1   | Status read                  |  |  |  |  |

| 0      | 0           | 1           | 0   | Write control data (command) |  |  |  |  |

# 3.2 Voltage Generator Circuit

# 3.3 Timing Diagram

| Item                       | Signal       | Symbol            | Condition             | Rating |      | Units |

|----------------------------|--------------|-------------------|-----------------------|--------|------|-------|

| Item                       | Signai       |                   | Condition             | Min    | Max. | Units |

| Address hold time          | 10           | t <sub>AH8</sub>  |                       | 0      |      | ns    |

| Address setup time         | A0 $t_{AW8}$ |                   |                       | 0      |      | ns    |

| System cycle time          | A0           | t <sub>CYC8</sub> |                       | 240    |      |       |

| Control L pulse width (WR) | WR           | t <sub>CCLW</sub> |                       | 80     |      | ns    |

| Control L pulse width (RD) | RD           | t <sub>CCLR</sub> |                       | 140    |      | ns    |

| Control H pulse width (WR) | WR           | t <sub>CCHW</sub> |                       | 80     |      | ns    |

| Control H pulse width (RD) | RD           | t <sub>CCHR</sub> |                       | 80     |      | ns    |

|                            |              | t <sub>DS8</sub>  |                       | 40     |      | ns    |

| RD access time             | D0 to        | t <sub>DH8</sub>  |                       | 10     |      | ns    |

| Output disable time        | D7           | t <sub>ACC8</sub> | C = 100  pE           |        | 70   | ns    |

|                            |              | t <sub>OH8</sub>  | C <sub>L</sub> =100pF | 5      | 50   | ns    |

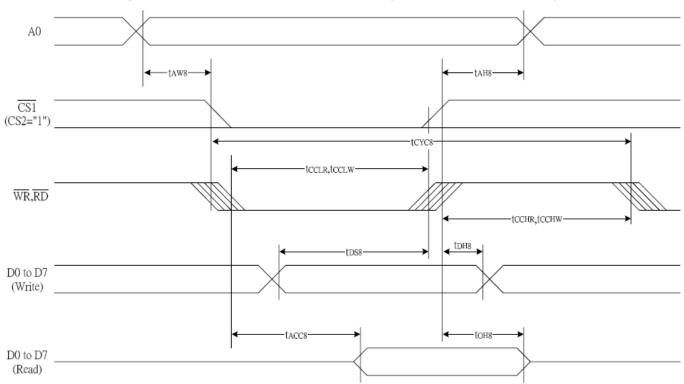

#### System Bus Read/Write Characteristics 1 (For the 8080 Series MPU)

| Item                       | Signal | Symbol            | Condition             | Rating |      | Units |

|----------------------------|--------|-------------------|-----------------------|--------|------|-------|

| nem                        | Signai |                   | Condition             | Min    | Max. | Units |

| Address hold time          | 4.0    | t <sub>AH8</sub>  |                       | 0      |      | ns    |

| Address setup time         | A0     | t <sub>AW8</sub>  |                       | 0      |      | ns    |

| System cycle time          | A0     | t <sub>CYC8</sub> |                       | 240    |      |       |

| Control L pulse width (WR) | WR     | t <sub>CCLW</sub> |                       | 80     |      | ns    |

| Control L pulse width (RD) | RD     | t <sub>CCLR</sub> |                       | 140    |      | ns    |

| Control H pulse width (WR) | WR     | t <sub>CCHW</sub> |                       | 80     |      | ns    |

| Control H pulse width (RD) | RD     | t <sub>CCHR</sub> |                       | 80     |      | ns    |

|                            |        | t <sub>DS8</sub>  |                       | 40     |      | ns    |

| RD access time             | D0 to  | t <sub>DH8</sub>  |                       | 10     |      | ns    |

| Output disable time        | D7     | t <sub>ACC8</sub> | C = 100 mE            |        | 70   | ns    |

|                            |        | t <sub>OH8</sub>  | C <sub>L</sub> =100pF | 5      | 50   | ns    |

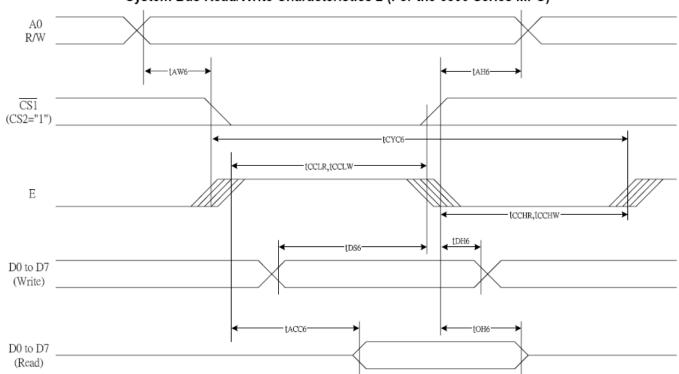

#### System Bus Read/Write Characteristics 2 (For the 6800 Series MPU)

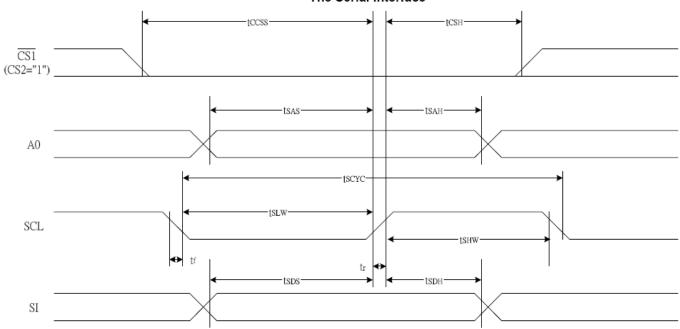

| Item                | Signal | Symbol | Condition | Rating |      | Luita |

|---------------------|--------|--------|-----------|--------|------|-------|

|                     |        |        |           | Min    | Max. | Units |

| Serial Clock Period | SCL    | Тѕсус  |           | 50     |      | ns    |

| SCL "H" pulse width |        | Tshw   |           | 25     |      | ns    |

| SCL "L" pulse width |        | TSLW   |           | 25     |      | ns    |

| Address setup time  | A0     | TSAS   |           | 20     |      | ns    |

| Address hold time   |        | Tsah   |           | 10     |      | ns    |

| Data setup time     | SI     | Tsds   |           | 20     |      | ns    |

| Data hold time      |        | TSDH   |           | 10     |      | ns    |

| CS-SCL time         | CS     | Tcss   |           | 20     |      | ns    |

| CS-SCL time         |        | Tcsh   |           | 40     |      | ns    |

# 4. NOTES

<u>Safety</u>

• If the LCD panel breaks, be careful not to get the liquid crystal in your mouth. If the liquid crystal touches your skin or clothes, wash it off immediately using soap and plenty of water.

### Handling

- Avoid static electricity as this can damage the CMOS LSI.

- The LCD panel is plate glass; do not hit or crush it.

- Do not remove the panel or frame from the module.

- The polarizing plate of the display is very fragile; handle it very carefully

## Mounting and Design

- Mount the module by using the specified mounting part and holes.

- To protect the module from external pressure, leave a small gap by placing transparent plates (e.g. acrylic or glass ) on the display surface, frame, and polarizing plate

- Design the system so that no input signal is given unless the power-supply voltage is applied.

- Keep the module dry. Avoid condensation, otherwise the transparent electrodes may break.

#### <u>Storage</u>

- Store the module in a dark place where the temperature is 25 °C±10 °C and the humidity below 65% RH.

- Do not store the module near organic solvents or corrosive gases.

- Do not crush, shake, or jolt the module (including accessories).

## Cleaning

- Do not wipe the polarizing plate with a dry cloth, as it may scratch the surface.

- Wipe the module gently with soft cloth soaked with a petroleum benzine.

- Do not use ketonic solvents (ketone and acetoe) or aromatic solvents (toluene and xylene), as they may damage the polarizing plate.