10.05.2022

# **Revision Status**

| Version | Revise Date | Page    | Content                                                                    | Modified By |

|---------|-------------|---------|----------------------------------------------------------------------------|-------------|

| 0       | 31.08.2018  |         | First issued                                                               |             |

| 1       | 31.08.2018  | 4       | Modify polarizer mode                                                      |             |

| 2       | 08.10.2018  | 4,10,12 | Add sample NO.; Modify VoP                                                 |             |

| 3       | 17.10.2018  | 4,5     | Remove sample NO.;<br>Modify UL model and the location of<br>code-spraying |             |

| 4       | 08.11.2018  | 15      | Increase each temperature refresh<br>time and drive voltage                |             |

| 5       | 14.12.2021  | 5       | Modify module Specification                                                |             |

| 6       | 10.05.2022  | 18      | Modify Packing instruction                                                 |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

|         |             |         |                                                                            |             |

# **Table of Contents**

| Nc  | ). | Contents Page                  | ge |

|-----|----|--------------------------------|----|

|     |    |                                |    |

| 1.  | ТЕ | ECHNOLOGY DESCRIPTION          | 4  |

| 2.  | ΤY | PICAL APPLICATIONS             | 4  |

| 3.  | GE | ENERAL DESCRIPTION             | 4  |

| 4.  | M  | ECHANICAL SPECIFICATIONS       | 4  |

| 5.  | IN | VTERFACE SIGNALS               | 6  |

| 6.  | AI | BSOLUTE MAXIMUM RATINGS        | 9  |

| 7.  | EL | LECTRICAL SPECIFICATIONS       | 10 |

| 8.  | OP | PTICAL CHARACTERISTICS AT 25°C | 15 |

| 9.  | LC | CD COSMETIC CONDITIONS         | 16 |

| 10. | HA | ANDLING PRECAUTION             | 17 |

# 1. Technology Description

BCD (Bi-stable Cholesteric Display) is a sunlight readable reflective LCD with extremely low power consumption characteristics. Due to the non-volatile memory feature of the technology, zero power is required to retain the image of the display. Energy is only required to change the displayed image. No backlighting is required, only ambient lighting from the surrounding is required. Readability when under direct sunlight is excellent and good contrast from viewing at very wide angles are possible.

# **2.** Typical Applications

This module is intended for general purpose graphic and character display applications. Suggested uses include instrumentation, remote control, electronic product or price label, point of sale display, general purpose indoor or outdoor signage and information display.

# **3.** General Description

The features of LCD are as follows

- \* Passive matrix bistable cholesteric LCD graphic module

- \* Color : Black & Yellow

- \* Display mode : BCD

- \* Driver/Controller IC : SSD1603

- \* Interface Input Data : 4-wires serial interface

- \* Driving scheme : Special BCD driving scheme

- \* Driving Method : 1/64 Duty,static

- \* Viewing Direction : Full viewing

- \* Backlight : Without

- \* Polarizer mode : Without polarizer

- \* Sample NO. : G1206ZDTRNFG-C0\_01/20181005

# 4. Mechanical Specifications

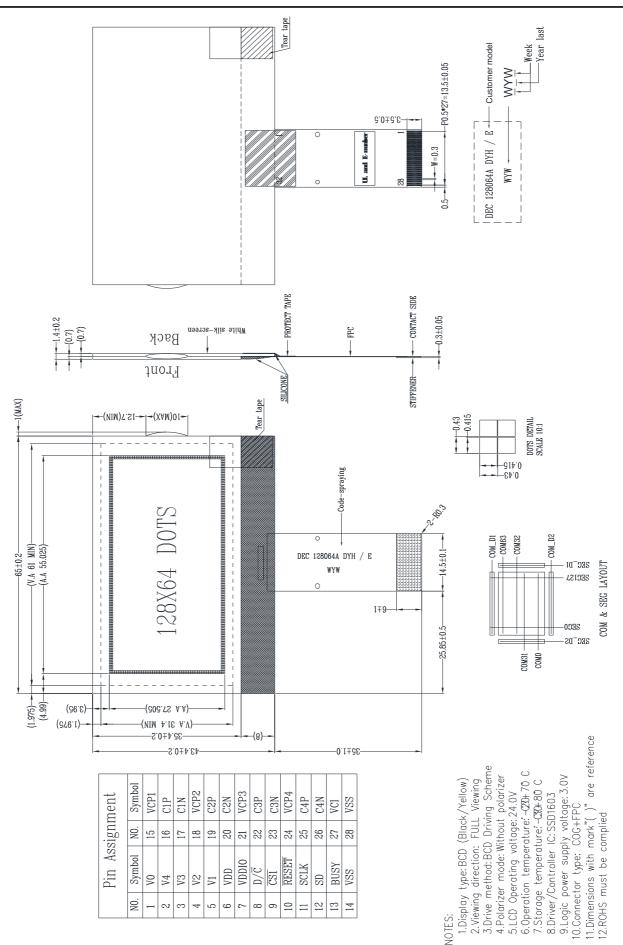

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

| Item           | Specification        | Unit |

|----------------|----------------------|------|

| Module Size    | 65.00 x 43.40 x 1.40 | mm   |

| Viewing Area   | 61 MIN x 31.4 MIN    | mm   |

| Active Area    | 55.025 x 27.505      | mm   |

| Number of Dots | 128 x 64 Dots        | -    |

| Dot Size       | 0.415 x 0.415        | mm   |

| Dot Pitch      | 0.43 x 0.43          | mm   |

#### Table 1

Figure 1: Module Specification

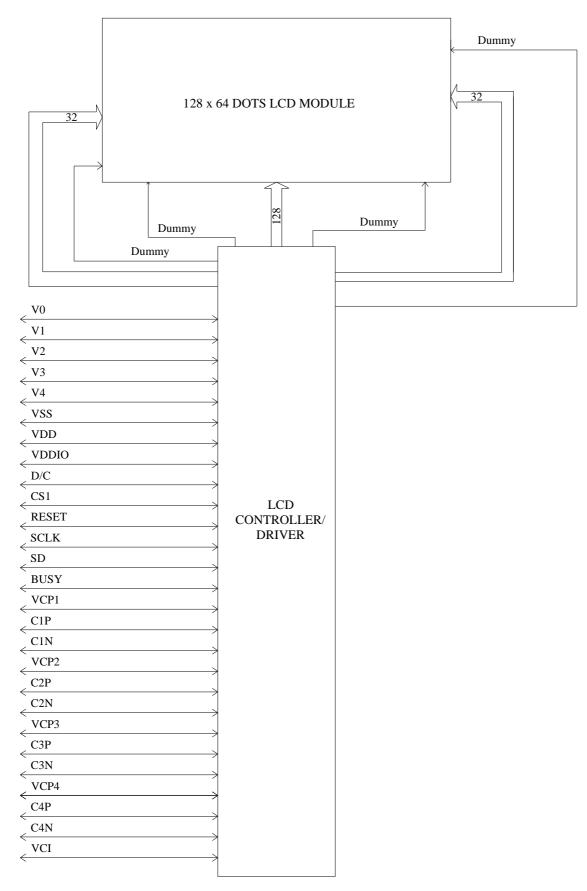

# 5. Interface Signals

|         | ice Signals | Table 2                                                                                                                                                                                                                                 |

|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO. | SYMBOL      | FUNCIONS                                                                                                                                                                                                                                |

| 1       | V0          | It is the high voltage power input pin and panel driving voltage.<br>It should be connected to VCP1.                                                                                                                                    |

| 2       | V4          | Panel driving voltage. If bias divider is enabled with the presence of V0. The voltage is equal to $1/N * V0$ , where N is equal to the Bias ratio Setting.                                                                             |

| 3       | V3          | Panel driving voltage. If bias divider is enabled with the presence of V0. The voltage is equal to $2/N * V0$ , where N is equal to the Bias ratio Setting.                                                                             |

| 4       | V2          | Panel driving voltage. If bias divider is enabled with the presence of V0.<br>The voltage is equal to $(N-2)/N * V0$ , where N is equal to the Bias ratio Setting.                                                                      |

| 5       | V1          | Panel driving voltage. If bias divider is enabled with the presence of V0.<br>The voltage is equal to $(N-1)/N * V0$ , where N is equal to the Bias ratio Setting.                                                                      |

| 6       | VDD         | This pin is the system power supply pin of the logic block.                                                                                                                                                                             |

| 7       | VDDIO       | Power supply for interface logic level. It should be match with the MCU interface voltage level. It must always be equal or lower than VDD.                                                                                             |

| 8       | D/C         | This pin is Data/Command control pin.<br>A high at D/C indicates data input while a low at D/C indicates command input.                                                                                                                 |

| 9       | CS1         | These pins are the chip select inputs for communication between MCU.<br>To select the chip CS1# must be low and CS2 must set high.<br>For serial mode, it is needed to select the chip which CS1# must be low and<br>CS2 must set high. |

| 10      | RESET       | This pin is the reset signal input. Initialization of the chip is started once this pin is pulled low. Minimum pulse width for reset sequence is 20us.                                                                                  |

| 11      | SCLK        | In serial interface mode, D1 is the serial data input (SDIN), D0 is the serial clock                                                                                                                                                    |

| 12      | SD          | input, (SCLK).                                                                                                                                                                                                                          |

| 13      | BUSY        | A high level indicates busy status (output driving waveform) of the driver.                                                                                                                                                             |

| 14      | VSS         | Ground.                                                                                                                                                                                                                                 |

| 15      | VCP1        | DC/DC output voltage. Connect with a capacitor to VSSC.<br>It should be connected to V0.                                                                                                                                                |

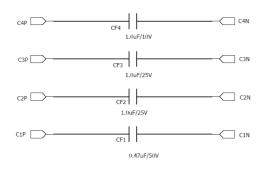

| 16      | C1P         | DC/DC flying capacitor terminal.                                                                                                                                                                                                        |

| 17      | C1N         | Connect a capacitor between C1N and C1P.                                                                                                                                                                                                |

| 18      | VCP2        | DC/DC intermediate output voltage. Connect with a capacitor to VSSC.<br>If using external mode with HV buffer enabled, it should be connected to V0.                                                                                    |

| 19      | C2P         | DC/DC flying capacitor terminal.                                                                                                                                                                                                        |

| 20      | C2N         | Connect a capacitor between C2N and C2P.                                                                                                                                                                                                |

| 21      | VCP3        | DC/DC intermediate output voltage. Connect with a capacitor to VSSC.                                                                                                                                                                    |

| 22      | C3P         | DC/DC flying capacitor terminal.                                                                                                                                                                                                        |

| 23      | C3N         | Connect a capacitor between C3N and C3P.                                                                                                                                                                                                |

| 24      | VCP4        | DC/DC intermediate output voltage. Connect with a capacitor to VSSC.                                                                                                                                                                    |

| 25      | C4P         | DC/DC flying capacitor terminal.                                                                                                                                                                                                        |

| 26      | C4N         | Connect a capacitor between C4N and C4P.                                                                                                                                                                                                |

| 27      | VCI         | Power supply for DC-DC converter and analog part of the chip.<br>It should be connected to VDD.                                                                                                                                         |

| 28      | VSS         | Ground.                                                                                                                                                                                                                                 |

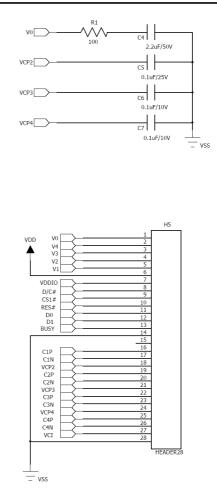

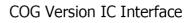

Figure 2: Block Diagram

# 6. Absolute Maximum Ratings

#### 6.1 Electrical Maximum Ratings-For IC Only

| Parameter        | Symbol            | Conditions    | Min.                  | Max.                    | Unit |

|------------------|-------------------|---------------|-----------------------|-------------------------|------|

|                  | V <sub>DD</sub>   |               | -0.3                  | +3.6                    | V    |

| Cummber) (altama | V <sub>DDIO</sub> | TA=+25℃,      | -0.3                  | Min(VDD+0.5,+3.6)       | V    |

| Supply Voltage   | Vo                | Referenced to | -0.3                  | +38                     | V    |

|                  | V <sub>CI</sub>   | $V_{SS} = 0V$ | -0.3                  | +3.6                    | V    |

| Input Voltage    | V <sub>in</sub>   |               | V <sub>ss</sub> - 0.3 | V <sub>DDIO</sub> + 0.3 | V    |

Table3

Note1: TA = +25 °C.

Note2: The maximum applicable voltage on any pin with respect to VSS (0V).

Note3: The modules may be destroyed if they are used beyond the absolute maximum ratings.

#### 6.2 Environmental Condition

#### Table4

| Item                                   | Opera<br>temper<br>(Top                    | ature                 | tempe                | rage<br>erature<br>stg) | Remark          |

|----------------------------------------|--------------------------------------------|-----------------------|----------------------|-------------------------|-----------------|

|                                        | Min.                                       | Max.                  | Min.                 | Max.                    |                 |

| Ambient temperature                    | -20°C                                      | +70°C                 | -30°C                | +80°C                   | Dry             |

| Humidity                               | 90% max. R<br>< 50% RH f<br>temperature    | for $40^{\circ}C < T$ | 40°C<br>`a ≤ Maximur | n operating             | No condensation |

| Packing<br>vibration(GB/T5170.14-2009) | Frequency ra<br>Acceleration<br>X,Y,Z 30 m | of gravity:5          | 3 directions         |                         |                 |

Note : Product cannot sustain at extreme storage conditions for long time.

# 7. Electrical Specifications

### 7.1 Typical Electrical Characteristics

At Ta = 25 °C, VDD = +3.0V± 5%, VSS=0V.

#### Table5

| Parameter                    | Symbol          | Conditions | Min.                 | Тур. | Max.                 | Unit |

|------------------------------|-----------------|------------|----------------------|------|----------------------|------|

| Supply voltage               | VDD-VSS         |            | 2.7                  | 3.0  | 3.5                  | V    |

| Supply voltage<br>(System)   | VCI-VSS         |            | VDD                  | -    | 3.5                  | V    |

| (Oystern)                    | VLCD            |            | -                    | 26.0 | -                    | V    |

| Input signal<br>voltage low  | VIL             |            | 0                    | -    | 0.2V <sub>DDIO</sub> | V    |

| Input signal<br>voltage high | V <sub>IH</sub> |            | 0.8V <sub>DDIO</sub> | -    | V <sub>DDIO</sub>    | V    |

|                              | IDD             | VDD=3.0V   | -                    | 0.5  | -                    | mA   |

| Supply current               | ICI             | VCI=3.0V   | -                    | 0.9  | 2.0                  | mA   |

\* Internally Generated

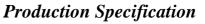

#### 7.2 TIMING Specifications

At Ta = +25 °C, VDD = VCI = VDDIO =  $+3.0V \pm 5\%$

#### Table 6

| Symbol             | Parameter                             | Min | Тур | Max | Unit |

|--------------------|---------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time                      | 60  | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                    | 10  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                     | 20  | -   | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                 | 30  | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                  | 30  | -   | -   | ns   |

| T <sub>CLKL</sub>  | Clock Low Time                        | 30  | -   | -   | ns   |

| T <sub>CLKH</sub>  | Clock High Time                       | 30  | -   | -   | ns   |

| t <sub>css</sub>   | Chip Select Setup Time (for D7 input) | 30  | -   | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time (for D0 input)  | 30  |     | -   | ns   |

| t <sub>R</sub>     | Rise Time                             | -   | -   | 10  | ns   |

| t <sub>F</sub>     | Fall Time                             | -   | -   | 10  | ns   |

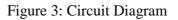

Figure 4:Timing characteristic of 4-wires Serial Interface

## 7.3 COMMAND TABLE

7.3.1. Command Table

#### (D/C# = 0, R/W#(WR#) = 0, E=1(RD# = 1) unless specific setting is stated)

| D/C | Hex              | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub>                   | D <sub>3</sub>                   | D <sub>2</sub>                   | D <sub>1</sub>                   | D <sub>0</sub>      | Command                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|------------------|----------------|----------------|----------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|---------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 10 – 1F          | 0              | 0              | 0              | 1                                | A3                               | A <sub>2</sub>                   | A <sub>1</sub>                   | Ao                  | Set column address                  | Set the higher nibble of the column address register<br>using $A_3A_2A_1A_0$ as data bits. The higher nibble of<br>column address is reset to 0000b after POR.<br>[POR=10 <sub>HEX</sub> ]<br>Set the lower nibble of the column address register                                                                                                                                                                                                                                                                                                                                                                           |

|     |                  |                |                |                |                                  |                                  |                                  |                                  |                     |                                     | using $B_3B_2B_1B_0$ as data bits. The lower nibble of column address is reset to 0000b after POR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0   |                  | 0              | 0              | 0              | 0                                | B <sub>3</sub>                   | B <sub>2</sub>                   | B <sub>1</sub>                   | Bo                  |                                     | [POR=00 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | 2A – 2F          | 0              | 0              | 1              | 0                                | 1                                | X <sub>2</sub>                   | 1                                | X <sub>0</sub>      | Set Power Control<br>Register       | X <sub>2</sub> =0: turns off Charge Pump<br>X <sub>2</sub> =1: turns on Charge Pump<br>X <sub>0</sub> = 0: turns off Bias Voltage buffer<br>X <sub>0</sub> =1: turns on Bias Voltage buffer<br>[POR=2A <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 31               | 0              | 0              | 1              | 1                                | 0                                | 0                                | 0                                | 1                   | Driving update                      | Update RAM content to the screen through<br>segment and common pins.<br>Driving sequence is always in:<br>VA clearing phase →Idle 1 phase → AA clearing<br>phase → Idle 2 phase → Driving phase                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | 32               | 0              | 0              | 1<br>¥c        | 1                                | 0                                | 0                                | 1                                | 0                   | Driving Scheme                      | Driving Scheme Setting<br>Active Area Control after clearing<br>$X_6X_5 = 01$ , Active Area is responsible to data 1<br>$X_6X_5 = 11$ , Active Area is responsible to data 0<br>Border Control after clearing<br>$X_4 = X_1 = 0$ , Border is responsible to data 0<br>$X_4 = X_1 = 0$ , Border is responsible to data 1<br>$X_3$ : driving polarity<br>0: M starts as 1 at Driving phase<br>1: M starts as 0 at Driving phase<br>1: M starts as 1 at Clearing phase<br>1: M starts as 0 at Clearing phase |

| 0   | 40 – 7F          | 0              | X <sub>6</sub> | X5<br>X5       | X <sub>4</sub><br>X <sub>4</sub> | X <sub>3</sub><br>X <sub>3</sub> | $X_2$<br>$X_2$                   | X <sub>1</sub><br>X <sub>1</sub> | X <sub>0</sub>      | Set Display Start                   | Display start line register is reset to 000000 after                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |                  |                |                |                |                                  |                                  |                                  |                                  |                     | Line                                | POR for all MUX modes. [POR=40 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | 80               | 1              | 0              | 0<br>0         | 0                                | 0                                | 0                                | 0                                | 0                   | Set the control                     | Set the control scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 00<br>P(4:01     | 0<br>0         | 0<br>0         | 0              | 0<br>B4                          | 0<br>B₃                          | 0                                | B <sub>1</sub>                   | 0<br>B₀             | scheme                              | P[4:0]: V/A Clearing Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0   | B[4:0]           | 0              | 0              | 0              |                                  |                                  | B <sub>2</sub><br>C <sub>2</sub> |                                  |                     |                                     | B[4:0] : VA Clearing Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0   | C[4:0]<br>D[4:0] | 0              | 0              | 0              | D <sub>4</sub>                   | $D_3$                            | $D_2$                            | $D_1$                            | $D_0$               |                                     | C[4:0]:Idle 1 Duration<br>D[4:0]:AA Clearing Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | E[4:0]           | 0              | 0              | 0              | E <sub>4</sub>                   | D₃<br>E₃                         | $E_2$                            | E <sub>1</sub>                   | E <sub>0</sub>      |                                     | E[4:0] : Idle 2 Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | F[4:0]           | 0              | 0              | 0              | F <sub>4</sub>                   | E3<br>F3                         | $F_2$                            | F <sub>1</sub>                   | F <sub>0</sub>      |                                     | F[4:0] : Driving Duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | G[6:1]           | 0              | G <sub>6</sub> | 0<br>G₅        | G <sub>4</sub>                   | G <sub>3</sub>                   | G <sub>2</sub>                   | G1                               | 0                   |                                     | G[6:1] : Clearing Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0   | H[6:1]           | 0              | H <sub>6</sub> | H <sub>5</sub> | H <sub>4</sub>                   | H <sub>3</sub>                   | H <sub>2</sub>                   | H <sub>1</sub>                   | õ                   |                                     | H[6:1] : Driving Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0   | 93               | 1              | 0              | 0<br>0         | 1<br>0                           | 0<br>X <sub>3</sub>              | 0<br>X <sub>2</sub>              | 1<br>X <sub>1</sub>              | 1<br>X <sub>0</sub> | Set view area phase<br>repeat times | $X_3X_2X_1X_0$ is Repeat time setting<br>*Remark: If VA clearing phase repeat time is set to<br>0, it is also needed to set the idle 1 phase repeat<br>time to 0. [POR=01 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0   | 94               | 1<br>0         | 0              | 0              | 1                                | 0<br>X <sub>3</sub>              | 1<br>X <sub>2</sub>              | 0<br>X <sub>1</sub>              | 0<br>X₀             | Set idle 1 phase<br>repeat times    | X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> is Repeat time setting<br>*Remark: If Idle 1 phase repeat time is set to 0, it is<br>also needed to set the VA clearing phase repeat<br>time to 0. [POR=01 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | 95               | 1              | 0              | 0              | 1                                | 0                                | 1                                | 0                                | 1                   | Set active area                     | $X_3X_2X_1X_0$ is Repeat time setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   |                  | 0              | 0              | 0              | 0                                | С<br>Х <sub>3</sub>              | ,<br>Х2                          | 0<br>X <sub>1</sub>              | '<br>X₀             | clearing phase<br>repeat times      | *Remark: If AA clearing phase repeat time is set to 0, it is also needed to set the idle2 phase repeat time to 0. [POR=01 $\mu$ EX]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0   | 96               | 1              | 0              | 0              | 1                                | 0                                | 1                                | 1                                | 0                   | Set idle 2 phase                    | $X_3X_2X_1X_0$ is Repeat time setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   |                  | 0              | 0              | 0              | 0                                | 0<br>Х <sub>3</sub>              | Т<br>Х2                          | Ч<br>Х1                          | X <sub>0</sub>      | repeat times                        | *Remark: If Idle 2 phase repeat time is set to 0, it is<br>also needed to set the AA clearing phase repeat time<br>to 0. $[POR=01 \text{ Hex}]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | 97               | 1              | 0              | 0              | 1                                | 0                                | 1                                | 1                                | 1                   | Set drive phase                     | $X_3X_2X_1X_0$ is Repeat time setting [POR=01 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0   |                  | 0              | 0              | 0              | 0                                | X <sub>3</sub>                   | X2                               | Х1                               | X₀                  | repeat times                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | A0 – A1          | 1              | 0              | 1              | 0                                | 0                                | 0                                | 0                                | X <sub>0</sub>      | Set Segment Re-<br>map              | X₀=0: Column address 00h is mapped to SEG0<br>X₀=1: Column address 83h is mapped to SEG0<br>[POR=A0 <sub>HEX</sub> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# **Production Specification**

| D/C | Hex      | D <sub>7</sub> | D <sub>6</sub> | D₅             | D4             | D <sub>3</sub> | D <sub>2</sub>        | D <sub>1</sub> | D₀             | Command                  | Description                                                                                                                          |

|-----|----------|----------------|----------------|----------------|----------------|----------------|-----------------------|----------------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0   | A2       | 1              | 0              | 1              | 0              | 0              | 0                     | 1              | 0              | Set LCD Bias             | $X_2X_1X_0=000: 1/9$                                                                                                                 |

| Ŭ   | /        |                | ľ              | 1.             | ľ              | ľ              | ľ                     | Ι.             | ľ              |                          | $X_2X_1X_0=001: 1/8,$                                                                                                                |

|     |          |                |                |                |                |                |                       |                |                |                          | X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> =010: 1/7,                                                                              |

|     |          |                |                |                |                |                |                       |                |                |                          | X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> =011: 1/6,                                                                              |

|     |          |                |                |                |                |                |                       |                |                |                          | X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> =100: 1/5,<br>X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> =111: 1/4                    |

|     |          |                |                |                |                |                |                       |                |                |                          | /2/1/0-111.1/4<br>[POR=00 <sub>HEX</sub> ]                                                                                           |

| 0   | 4.0      | 0              | 0              | 0              | 0              | 0              | X <sub>2</sub>        | X <sub>1</sub> | X <sub>0</sub> |                          |                                                                                                                                      |

| 0   | A3       | 1              | 0              | 1              | 0              | 0              | 0                     | 1              | 1              | Set analog control       | X <sub>4</sub> X <sub>3</sub> = 00: Disable<br>X <sub>4</sub> X <sub>3</sub> = 11: Enable                                            |

|     |          |                |                |                |                |                |                       |                |                |                          | $X_1 = 0$ : Standard BIAS VOLTAGE Buffer Setting                                                                                     |

|     |          |                |                |                |                |                |                       |                |                |                          | $X_1 = 1$ : Extra BIAS VOLTAGE Buffer Setting                                                                                        |

|     |          |                |                |                |                |                |                       |                |                |                          | [POR=00 <sub>HEX</sub> ]                                                                                                             |

| 0   |          | 0              | 0              | 0              | <b>X</b> 4     | X <sub>3</sub> | 0                     | <b>X</b> 1     | 0              |                          |                                                                                                                                      |

| 0   | A4 – A5  | 1              | 0              | 1              | 0              | 0              | 1                     | 0              | X <sub>0</sub> | Set Entire Display       | X₀=0: normal display                                                                                                                 |

|     |          |                |                |                |                |                |                       |                |                | On/Off                   | X <sub>0</sub> =1: entire display on                                                                                                 |

| 0   | A6 – A7  | 1              | 0              | 1              | 0              | 0              | 1                     | 1              | X <sub>0</sub> | Set Normal/Reverse       | [POR=A4 <sub>HEX</sub> ]<br>X₀=0: normal display                                                                                     |

| 0   | A0 - A7  | 1              | ľ              | 1'             | 0              | ľ              | '                     | l' -           | <b>^</b> 0     | Display                  | $X_0=0$ . Horman display<br>$X_0=1$ : reverse display                                                                                |

|     |          |                |                |                |                |                |                       |                |                | Display                  | [POR=A6 <sub>HEX</sub> ]                                                                                                             |

| 0   | A8       | 1              | 0              | 1              | 0              | 1              | 0                     | 0              | 0              | Set Multiplex Ratio      | To select multiplex ratio N MUX                                                                                                      |

| 0   |          | 0              | X <sub>6</sub> | X <sub>5</sub> | <b>X</b> 4     | X <sub>3</sub> | X <sub>2</sub>        | X <sub>1</sub> | Xo             |                          | $X_6X_5X_4X_3X_2X_1X_0 = N$ from 2 to 64                                                                                             |

|     |          |                |                |                |                |                |                       |                | <u> </u>       |                          | [POR=40 <sub>HEX</sub> ]                                                                                                             |

| 0   | A9       | 1              | 0              | 1              | 0              | 1              | 0                     | 0              | 1              | Analog Control Auto      | X <sub>0</sub> = 0: OFF                                                                                                              |

|     |          |                |                |                |                |                |                       |                |                | ON/OFF                   | X <sub>0</sub> = 1: ON<br>[POR=00 <sub>HEX</sub> ]                                                                                   |

| 0   |          | 0              | 0              | 0              | 0              | 0              | 0                     | 0<br>0         | X <sub>0</sub> | RAM Read/Write           | X <sub>0</sub> = 0: RAM read/write horizontal                                                                                        |

| 0   | AD       | 1              | 0              | 1              | 0              | 11             | 1                     | 0              | 1              | Direction                | $X_0= 0$ : RAM read/write norizontal $X_0= 1$ : RAM read/write vertical                                                              |

| 0   |          | 0              | 0              | 0              | 0              | 0              | 0                     | 0              | X <sub>0</sub> | Direction                | [POR=00 <sub>HEX</sub> ]                                                                                                             |

| 0   | AE       | 1              | 0              | 1              | 0              | 1              | 1                     | 1              | 0              | Set Auto Charge          | X <sub>6</sub> X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> :                           |

|     |          |                |                |                |                |                |                       |                |                | pump Threshold           | Auto Charge Pump Threshold                                                                                                           |

|     |          |                |                |                |                |                |                       |                |                | Value                    | If contrast setting > threshold, 16X Charge Pump                                                                                     |

|     |          |                |                |                |                |                |                       |                |                |                          | setting would be selected,                                                                                                           |

| 0   |          | 0              | X <sub>6</sub> | <b>X</b> 5     | $X_4$          | X₃             | X <sub>2</sub>        | X <sub>1</sub> | X <sub>0</sub> |                          | Otherwise, 8X Charge Pump is used.<br>[POR=20 <sub>HEX</sub> ]                                                                       |

| 0   | B0 – B7  | 1              | 0              | 1              | 1              | 0              | <b>X</b> <sub>2</sub> | X <sub>1</sub> | X <sub>0</sub> | Set Page Address         | Set GDDRAM Page Address (0-7) for read/write                                                                                         |

| Ŭ   | 50 51    |                | ľ              | 1.             | l'             | ľ              | <u> </u>              |                |                |                          | using $X_2X_1X_0$                                                                                                                    |

|     |          |                |                |                |                |                |                       |                |                |                          | [POR=B0 <sub>HEX</sub> ]                                                                                                             |

| 0   | C0 / C8  | 1              | 1              | 0              | 0              | <b>X</b> 3     | 0                     | 0              | 0              | Set COM Output           | X₃=0: normal mode                                                                                                                    |

|     |          |                |                |                |                |                |                       |                |                | Scan Direction           | X <sub>3</sub> =1: remapped mode                                                                                                     |

|     |          |                |                |                |                |                |                       |                |                |                          | COM0 to COM [N-1] becomes COM [N-1] to COM0 when Multiplex ratio is equal to N.                                                      |

|     |          |                |                |                |                |                |                       |                |                |                          | [POR=CO <sub>HEX</sub> ]                                                                                                             |

| 0   | D3       | 1              | 1              | 0              | 1              | 0              | 0                     | 1              | 1              | Set Display Offset       | After setting MUX ratio less than default value, data                                                                                |

|     |          |                |                |                |                |                |                       |                |                |                          | will be displayed at the beginning/towards the end                                                                                   |

|     |          |                |                |                |                |                |                       |                |                |                          | of display matrix.                                                                                                                   |

|     |          |                |                |                |                |                |                       |                |                |                          | To move display towards Row 0 by L,<br>X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> = L |

|     |          |                |                |                |                |                |                       |                |                |                          | To move display away from Row 0 by L,                                                                                                |

|     |          |                |                |                |                |                |                       |                |                |                          | $X_5X_4X_3X_2X_1X_0 = Y - L$                                                                                                         |

|     |          |                |                |                |                |                |                       |                |                |                          | Note: max value of L = Y – display MUX                                                                                               |

| 0   |          | 0              |                | V-             | v.             | V.             | V.                    | v.             | Xo             |                          | Y represents POR default MUX                                                                                                         |

| 0   | E2       | 1              | 0              | X <sub>5</sub> | X <sub>4</sub> | X₃<br>0        | X <sub>2</sub>        | X <sub>1</sub> | ∧₀<br>0        | Software Reset           | [POR=00 <sub>HEX</sub> ]<br>Initialize internal status registers.                                                                    |

|     | L2       |                |                | Ľ              | -              | ľ              | 1                     |                |                |                          | milianze mierra status registers.                                                                                                    |

| 0   | E3       | 1<br>1         | 1              | 1              | 0<br>0         | 0              | 0                     | 1              | 1              | NOP                      | No operation                                                                                                                         |

| 0   | E3<br>E9 | 1              | 1              | 1              | 0              | 1              | 0                     | 1              | 1              | NOP<br>Set Bias Resistor | No operation<br>X <sub>7</sub> = 0: Disable                                                                                          |

| ľ   | 20       | ['             | ['             | ['             | ľ              | ['             | ľ                     | ľ              | ['             | Ladder                   | $X_7 = 0$ . Disable $X_7 = 1$ : Enable                                                                                               |

| 0   |          | <b>X</b> 7     | 0              | 0              | 0              | 0              | 1                     | 0              | 0              |                          | [POR=04 <sub>HEX</sub> ]                                                                                                             |

| 0   | F6       | 1              | 1              | 1              | 1              | 0              | 1                     | 1              | 0              | Set Internal             | X <sub>6</sub> = 0: Disable                                                                                                          |

|     |          |                |                |                |                |                |                       |                |                | Oscillator               | X <sub>6</sub> = 1: Enable                                                                                                           |

| 0   |          | 0<br>1         | X <sub>6</sub> | 0              | 0              | 0              | 0                     | 0<br>0         | 0              |                          | [POR=00 <sub>HEX</sub> ]                                                                                                             |

| U U | FD       | '              | ['             | 1'             | 1'             | 1'             | ['                    | ľ              | 1              | Lock/unlock driver       | X <sub>2</sub> = 0: unlock driver<br>X <sub>2</sub> = 1: lock driver                                                                 |

| 1   |          |                | 1              | I I            |                | 1              | 1                     |                | 1              |                          | Or unlock driver when hardware reset                                                                                                 |

|     |          |                |                |                | 1              |                |                       |                |                |                          |                                                                                                                                      |

| 1   |          |                | 1              | I I            |                | 1              | 1                     |                | 1              |                          | (No command or data will be written to driver when                                                                                   |

|     |          |                |                |                | 1              |                |                       | 1              |                |                          | the lock is high)                                                                                                                    |

| 0   | FE       | 0<br>1         | 0              | 0              | 1              | 0              | X <sub>2</sub>        | 1              | 0<br>0         | Set Clock Enable         | [POR=12 <sub>HEX</sub> ]<br>X <sub>7</sub> = 0: Disable                                                                              |

| ľ   |          | '              | ['             | ['             | ['             | ['             | ['                    | l' -           | ľ              | Set CIOCK ETIADLE        | $X_7=0$ . Disable $X_7=1$ : Enable                                                                                                   |

| 0   |          | <b>X</b> 7     | 0              | 0              | 0              | 0              | 0                     | 0              | 0              |                          | [POR=00 <sub>HEX</sub> ]                                                                                                             |

| Ľ   |          | ~/             | 17             | <b>1</b> 0     | . Ч            | 1              | 1                     | 1.2            | 17             |                          | -                                                                                                                                    |

7.3.2.Read Command Table

| (D/C# = 0, R/W#(WR#) = | 1, E=1(RD# = 0) unless | specific setting is stated) |

|------------------------|------------------------|-----------------------------|

|------------------------|------------------------|-----------------------------|

| D/C | Hex        | D7 | D <sub>6</sub> | D5 | D4 | D <sub>3</sub> | D2             | D1 | D <sub>0</sub> | Command                 | Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|------------|----|----------------|----|----|----------------|----------------|----|----------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 00 -<br>FF | X7 | X6             | X5 | 0  | X3             | X <sub>2</sub> | X1 | Xo             | Status Register<br>Read | $X_7=0$ : indicates the driver is ready for<br>command. $X_7=1$ : indicates the driver is Busy. $X_6=0$ : indicates normal segment mapping with<br>column address. $X_6=1$ : indicates reverse segment mapping<br>with column address. $X_5=0$ : indicates the display is ON. $X_5=1$ : indicates the display is OFF. $X_3X_2X_1X_0 = 0010$ , the 4-bit is fixed to 0010 which<br>could be used to identify as Device. |

### 7.4 Temperature Compensation

#### Table 7: TC Table

| _                    | View Area      | View Area Idle | Active Area    | Active Area   | Drive    |

|----------------------|----------------|----------------|----------------|---------------|----------|

| Temperature,<br>T(℃) | Clear Duration | Duration       | Clear Duration | Idle Duration | Duration |

| .( .)                | (ms)           | (ms)           | (ms)           | (ms)          | (ms)     |

| 50≪T<70              | 6              | 12             | 100            | 12            | 6        |

| 10≪T<50              | 18             | 12             | 100            | 12            | 18       |

| 0≪T<10               | 35             | 12             | 150            | 12            | 35       |

| -5≪T<0               | 50             | 12             | 200            | 12            | 50       |

| -10≪T<-5             | 80             | 12             | 250            | 12            | 80       |

| -15≪T<-10            | 150            | 12             | 350            | 12            | 150      |

| -20≪T<-15            | 350            | 12             | 700            | 12            | 350      |

Notes: For details, please reference to BCD application notes.

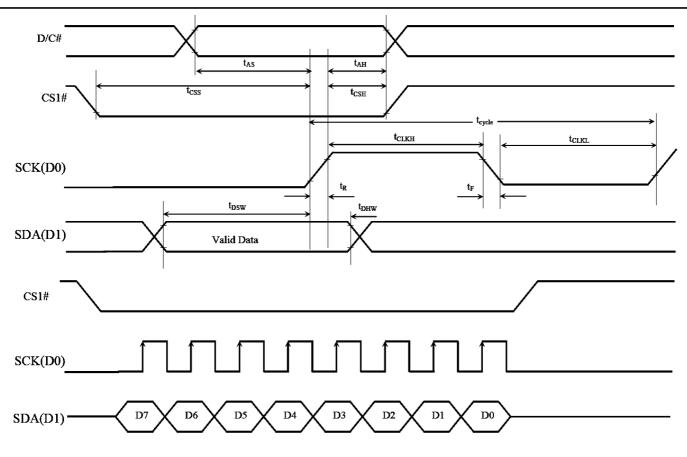

# 8. Optical Characteristics at 25°C

Table 8

| Item                                  | Symbol                         | Value |      |      | Unit | Condition                                             |                      |

|---------------------------------------|--------------------------------|-------|------|------|------|-------------------------------------------------------|----------------------|

|                                       |                                | Min.  | Тур. | Max. | Om   | Condition                                             |                      |

| Image<br>refresh time                 | -                              | -     | 2.4  | -    | S    | VDD= $3.0V$ ,<br>VLCD = $31.0V$<br>At Ta = - $20$ °C  |                      |

|                                       | -                              | -     | 2.2  | -    | S    | $VDD=3.0V,$ $VLCD=28.0V$ $At Ta = -10 \ ^{\circ}C$    |                      |

|                                       | -                              | _     | 2.0  | -    | S    | VDD=3.0V, $VLCD=26.8V$ $At Ta = 0 °C$                 |                      |

|                                       | -                              | -     | 1.8  | -    | S    | VDD= $3.0V$ ,<br>VLCD = $26.0V$<br>At Ta = $+5$ °C    |                      |

|                                       | -                              | -     | 1.8  | -    | S    | VDD= $3.0$ V,<br>VLCD = $26.0$ V<br>At Ta = + $25$ °C |                      |

|                                       | -                              | -     | 1.8  | -    | S    | VDD= $3.0$ V,<br>VLCD = $25.7$ V<br>At Ta = $+50$ °C  |                      |

|                                       | -                              | -     | 1.6  | -    | S    | VDD= $3.0V$ ,<br>VLCD = $25.0V$<br>At Ta = $+70$ °C   |                      |

| Contrast<br>ratio                     | CR                             | -     | 6    | -    | -    | -                                                     |                      |

| Optimum<br>viewing area<br>$Cr \ge 2$ | θ1(6 o'clock)                  | -     | 80   | -    |      | + 00                                                  | = 0° Vop=<br>Optimum |

|                                       | $\theta 2(12 \text{ o'clock})$ | -     | 80   | -    | DEG  | $\phi = 0^{\circ}$                                    |                      |

|                                       | φ1(3 o'clock)                  | -     | 80   | -    | DEG  | $\phi = 0^{\circ}$                                    | voltage              |

|                                       | φ2(9 o'clock)                  | -     | 80   | -    |      |                                                       | č                    |

Notes: The above data are for reference only.

#### 8.1 Optical Characteristics Definition

### 8.1.1 Viewing Angle

Figure 5

#### 8.1.2 Contrast Ratio

B1 = pixel luminance at stable dark state

B2 = pixel luminance at stable bright state

Contrast Ratio = B2/B1

# 9. LCD Cosmetic Conditions

LCD size of the product is small.

# **10. HANDLING PRECAUTION**

(1) Mounting Method

The panel of the LCD Module consists of two thin glass plates with polarizers which easily get damaged since the Module is fixed by utilizing fitting holes in the printed circuit board. Extreme care should be taken when handling the LCD Modules.

(2) Caution of LCD handling & cleaning

When cleaning the display surface, use soft cloth with solvent (recommended below) and wipe lightly.

- Isopropyl alcohol

- Ethyl alcohol

- Trichloro trifloro thane

- Do not wipe the display surface with dry or hard materials that will damage the polarizer surface. Do not use the following solvent:

- Water

- Ketone

- Aromatics

(3) Caution against static charge

- The LCD Module use C-MOS LSI drivers, so we recommend that you connect

- any unused input terminal to VDD or VSS, do not input any signals before power

- is turned on. And ground your body, Work/assembly table. And assembly equipment to protect against static electricity.

- (4) Packaging

- Modules use LCD elements, and must be treated as such. Avoid intense shock and falls from a height.

- To prevent modules from degradation. Do not operate or store them exposed directly to sunshine or high

- temperature/humidity.

- (5) Caution for operation

- It is indispensable to drive LCD's within the specified voltage limit since the higher voltage than the limit shorten LCD life. An electrochemical reaction due to direct current causes LCD deterioration, Avoid the use of direct current drive.

- Response time will be extremely delayed at lower temperature than the operating temperature range and on the other hand at higher temperature LCD's show dark color in them. However those phenomena do not mean malfunction or out of order with LCD's. Which will come back in the specified operating temperature range.

- If the display area is pushed hard during operation, some font will be abnormally displayed but it resumes normal condition after turning off once.

- A slight dew depositing on terminals is a cause for electro-chemical reaction resulting in terminal open circuit.

- Usage under the relative condition of 40°C, 50%RH or less is reequired.

#### (6) Storage

- In the case of storing for a long period of time (for instance.) For years) for the purpose or replacement use, The following ways are recommended.

- Storage in a polyethylene bag with sealed so as not to enter fresh air outside in it, And with no desiccant.

- Placing in a dark place where neither exposure to direct sunlight nor light is. Keeping temperature in the specified storage temperature range.

- Storing with no touch on polarizer surface by the anything else. (It is recommended to store them as they have been contained in the inner container at the time of delivery)

- (7) Safety

- It is recommendable to crash damaged or unnecessary LCD into pieces and wash off liquid crystal by using solvents such as acetone and ethanol.

- Which should be burned up later.

- (8) Other

- After the product shipped, any product quality issues must be feedback within three months, otherwise, we will not be responsible for the subsequent or consequential events.